- Handles All IEEE-488 1975/78 Functions

- Compatible with IEEE-488A 1980 Supplement

- Maximum Transfer Rate . . . Greater Than 360 Kilobytes/Second

- Talker and Listener Function (T, TE, L, LE)

- Automatic Source and Acceptor Handshakes (SH, AH)

- Controller with Pass Control

- System Controller Capabilities

- Device Trigger and Device Clear Capabilities (DT, DC)

- Optional Automatically Cleared 'Request Service Bit'

- Parallel and Serial Poll Facilities (PP)

- Remote/Local Function with Local Lockout (RL)

- Single or Dual Primary Addressing

- Secondary Address Capabilities

- Direct Interface to SN75160/161/162 Bus

Transceivers with No Additional Logic

- Compatible with Most Microprocessors

- Direct-Memory-Access Facilities

- Memory-Mapped Microprocessor Interface

- Temperature Range . . . −55 °C to 110 °C (S Suffix)

#### description

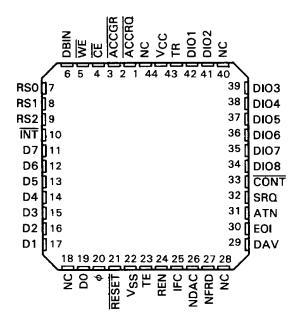

The SMJ9914A provides an interface between a Microprocessor System and the General Purpose Interface Bus (GPIB) specified in the IEEE-488 1975/78 standards and the IEEE-488A 1980 supplement. The device is controlled and configured through 8-bit memory-mapped registers and enables all aspects of the standards to be implemented, including talker, listener and controller. The functional block diagram is shown on page 3.

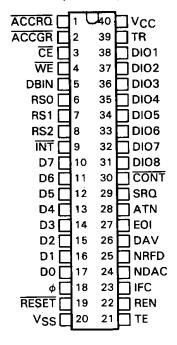

# JD PACKAGE (TOP VIEW)

#### FD PACKAGE (TOP VIEW)

PRODUCTION DATA documents contain information current as of publication data. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1986, Texas Instruments Incorporated

### SMJ9914A GPIB CONTROLLER

The GPIB is designed to allow up to 15 instruments within a localized area to communicate with each other over a common bus. Each device has a unique address, read from external switches at power-on, to which it responds. Information is transmitted by byte-serial bit-parallel format and may consist of either device-dependent data or interface messages, commonly referred to as data or command, respectively. A typical application is shown in Figure 1. Auxiliary commands are listed in Table 1.

Device data may be sent by any one device (the talker) and received by a number of other devices (listeners). Instructions, such as select range, select function, or measurement data for processing or printout, may be sent in this way.

The SMJ9914A performs the interface function between the microprocessor and GPIB bus and relieves the processor of the task of maintaining the IEEE protocol. By utilizing the interrupt capabilities of the device, the bus does not have to be continually polled, and fast responses to changes in the interface configuration can be achieved.

The GPIB input/output pins are connected to the IEEE-488 bus via bus tranceivers. The direction of data flow is controlled by the TE and CONT outputs generated on the SMJ9914A. The SN75160, 75161 and 75162 bus transceivers are designed specifically for use with a GPIB interface. The TE and CONT signals are routed within the devices so that the buffers on particular lines are controlled as required by the SMJ9914A. Other buffers may be used, but they may require a small amount of external logic, particularly around the EOI line buffer.

#### functional block diagram

FIGURE 1. TYPICAL SMJ9914A APPLICATION

### SMJ9914A GPIB CONTROLLER

#### pin descriptions

|       | PIN             | I/O              |                                                                                                                                                                                |

|-------|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.   | NAME            | (TYPE)           | DESCRIPTION                                                                                                                                                                    |

| 1     | ACCRO           | O <sup>†</sup>   | Access Request. This pin becomes active (low) to request a direct memory access.                                                                                               |

| 2     | ACCGR           | ı                | Access Granted. When received from the direct-memory-access control logic, this enables the byte onto the data bus. ACCGR must be high when not participating in DMA transfer. |

| 3     | CE              | l                | Chip Enable. $\overline{CE}$ allows access of read and write registers. If $\overline{CE}$ is high, D0-D7 are in high impedance unless $\overline{ACCGR}$ is low.              |

| 4     | WE              | ı                | Write Enable. When active (low), indicates to the SMJ9914A that data is being written to one of its registers.                                                                 |

| 5     | DBIN            | ı                | Data Bus In. An active (high) state indicates to the SMJ9914A that a read is about to be carried out by the MPU.                                                               |

| 6     | RS0             | 1                | Register Select Lines. Determine which register is addressed by the MPU during a read                                                                                          |

| 7     | RS1             | į ı              | or write operation.                                                                                                                                                            |

| 8     | RS2             | 1                | of Wite operation.                                                                                                                                                             |

| 9     | ĪNT .           | o‡               | Interrupt. Sent to the MPU to cause a branch to a service routine.                                                                                                             |

| 17-10 | D0-D7           | 1/0†             | Data transfer lines on the MPU side of the device. D0 is the most-significant bit.                                                                                             |

| 18    | φ               | l l              | Clock Input, 500 kHz to 5 MHz. Need not be synchronous to system clock.                                                                                                        |

| 19    | RESET §         | 1                | Initializes the SMJ9914A at power-on.                                                                                                                                          |

| 20    | V <sub>SS</sub> |                  | Ground reference voltage.                                                                                                                                                      |

| 21    | TE              | O <sup>†</sup>   | Talk Enable. Controls the direction of the transfer of the line transceivers. Logically, it is: [CACS + TACS + EIO.ATN.(CIDS + CADS) SWRST].                                   |

| 22    | REN             | 1/0¶             | Remote Enable. Sent by system controller to select control either from the front panel or from the IEEE bus.                                                                   |

| 23    | IFC             | 1/O¶             | Interface Clear. Sent by the system controller to set the interface system into a known quiescent state. The system controller becomes the controller in charge.               |

| 24    | NDAC            | 1/0†             | Not Data Accepted. Handshake line. Acceptor sets this false (high) when it has latched the data from the I/O lines.                                                            |

| 25    | NRFD            | 1/0†             | Not Ready For Data. Handshake line. Sent by acceptor to indicate readiness for the next byte.                                                                                  |

| 26    | DAV             | 1/0↑             | Data Valid. Handshake line controlled by source to show acceptors when valid data is present to the bus.                                                                       |

| 27    | EOI             | 1/0†             | End Or Identify. If ATN is false (high), this indicates the end of a message block. If ATN is true (low), the controller is requesting a parallel poll.                        |

| 28    | ATN             | 1/0†             | Attention. Sent by controller in charge. When true (low), interface commands are being sent over the DIO lines. When false (high), these lines carry data.                     |

| 29    | SRQ             | I/O <sup>†</sup> | Service Request. Set true (low) by a device to indicate a need for service.                                                                                                    |

| 30    | CONT            | O <sup>†</sup>   | Indicates (low) if a device is controller in charge. It is used to control direction of SRQ and ATN in pass control systems. Logically, it is (CIDS + CADS).                   |

| 31-38 | DIO8-DIO1       | 1/0†             | DIO8 through DIO1 are the data input/output lines on the GPIB side. These pins connect to the IEEE-488 bus via non-inverting transceivers.                                     |

| 39    | TR              | O <sup>†</sup>   | Trigger. Activated when the GET command is received over the interface or the fget command is given by the MPU.                                                                |

| 40    | V <sub>CC</sub> |                  | Supply voltage (5 V nominal).                                                                                                                                                  |

<sup>†</sup>Push-pull output

<sup>¶</sup>Open-drain output with internal pullup

<sup>&</sup>lt;sup>‡</sup>Open-drain output with no internal pullup

<sup>§</sup>The hardware RESET pin has the following effect on the SMJ9914A:

<sup>-</sup>Serial and Parallel Poll registers cleared

<sup>-</sup>All clear/set auxiliary commands cleared except 'swrst'

<sup>-&#</sup>x27;swrst' auxiliary command set. This holds the SMJ9914A in known states.

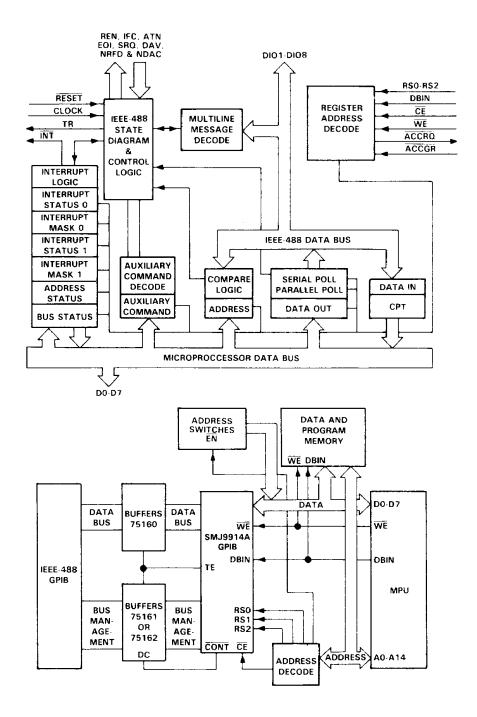

Communication between the microprocessor and SMJ9914A is carried out via memory-mapped registers. There are 13 registers within the SMJ9914A, 6 of which are read and 7 are write. These registers both pass control data to and get status information from the device. These registers are listed in Table 2 and shown in Figure 2.

The three least-significant address lines from the MPU are connected to register select lines RS0, RS1, and RS2 and determine the particular register selected. The high-order address lines are decoded by external logic to cause the  $\overline{\text{CE}}$  input to the SMJ9914A to be pulled low when any one of eight consecutive addresses are selected. Thus the internal registers appear to be situated at eight consecutive locations within the MPU address space. Reading or writing to these locations transfers information between the SMJ9914A and the microprocessor. Note that reading and writing to the same location will not access the same register within the SMJ9914A since they are either read-only or write-only registers. For example, a read operation with RS2-RS0 = 011 gives the current status of the GPIB interface control lines, whereas a write to this location loads the auxiliary-command register.

Each device on the bus interface is given a 5-bit address enabling it to be addressed as a talker or listener. This address is set on an external DIP switch (usually at the rear of an instrument) before power-on.

Typical SMJ9914A configuration utilizes registers 100 or 101 as an address switch register (see Table 2.). This register may consist of a DIP switch which drives the data lines via 3-state buffers when one of these addresses is read. This allows the host MPU to read a device address which is manually set and write this address into the address register of the SMJ9914A for device identification on the bus. The SMJ9914A responds by causing a My Address (MA) interrupt and entering the required addressed state when this address is detected on the GPIB data lines.

**TABLE 1. AUXILIARY COMMANDS**

|          |                          |       |     | C/S  |

|----------|--------------------------|-------|-----|------|

| MNEMONIC | DESCRIPTION              | CLEAR | SET | NA   |

|          |                          |       |     | CODE |

| dacr     | Release DAC holdoff      | 01    | 81  |      |

| dai      | Disable all interrupts   | 13    | 93  |      |

| feoi     | Send EOI with next byte  |       |     | 08   |

| fget     | Force group execute      |       |     |      |

|          | trigger                  | 06    | 86  |      |

| gts      | Go to standby            | İ     | 1   | OB   |

| hdfa     | Holdoff on all data      | 03    | 83  |      |

| hdfe     | Holdoff on EOI only      | 04    | 84  |      |

| lon      | Listen only              | 09    | 89  |      |

| nbaf     | New byte available false |       | ļ   | 05   |

| pts      | Pass through next        |       |     |      |

|          | secondary                |       |     | 14   |

| rhdf     | Release RFD holdoff      |       |     | 02   |

| rlc      | Release control          |       |     | 12   |

| rpp      | Request parallel poil    | 0E    | 8E  | ]    |

| rqc      | Request control          |       |     | 11   |

| rsv2     | Request service bit 2    | 18    | 98  |      |

| rtl      | Return to local          | 07    | 87  |      |

| shdw     | Shadow handshake         | 16    | 96  |      |

| sic      | Send interface clear     | OF    | 8F  | l i  |

| sre      | Send remote enable       | 10    | 90  | i l  |

| std1     | Short T1 settling time   | 15    | 95  |      |

| tca      | Take control             |       | ł   |      |

|          | asynchronously           |       |     | oc   |

| tcs      | Take control             |       |     |      |

|          | synchronously            |       |     | GO   |

| ton      | Talk only                | 0A    | 8A  |      |

| vstd1    | Very short T1 delay      | 17    | 97  |      |

**TABLE 2. REGISTER ADDRESSES**

| Α   | DDRES | S   | READ               | WRITE             |

|-----|-------|-----|--------------------|-------------------|

| RS2 | RS1   | RS0 | REGISTERS          | REGISTERS         |

| 0   | 0     | 0   | Interrupt Status 0 | Interrupt Mask 0  |

| 0   | 0     | 1   | Interrupt Status 1 | Interrupt Mask 1  |

| 0   | 1     | 0   | Address Status     | <b>‡</b>          |

| 0   | 1     | 1   | Bus Status         | Auxiliary Command |

| 1   | 0     | 0   | t                  | Address           |

| 1   | 0     | 1   | †                  | Serial Poll       |

| 1   | 1     | 0   | Command Pass Thru  | Parallel Poll     |

| 1   | 1     | 1   | Data In            | Data Out          |

<sup>&</sup>lt;sup>†</sup>The SMJ9914A host interface data lines will remain in the highimpedance state when these register locations are addressed. An Address Switch Register may therefore be included in the address space of the device at these locations.

<sup>&</sup>lt;sup>3</sup>This address is not decoded by the SMJ9914A. A write to this location will have no effect on the device, as if a write had not occurred.

#### reference documentation

- TMS9914A GPIB Controller User's Guide (SPPU013)

- TMS9914A General Purpose Interface Bus (GPIB) Controller Data Manual (MP033A)

| DATA-IN REGISTER       |     |     |      |      |      |      |      |      |      |            |     |  |

|------------------------|-----|-----|------|------|------|------|------|------|------|------------|-----|--|

| ADDRESS BIT ASSIGNMENT |     |     |      |      |      |      |      |      |      |            |     |  |

| RS2                    | RS1 | RS0 | DO   | D1   | D2   | D3   | D4   | D5   | D6   | <b>D</b> 7 |     |  |

| 1                      | 1   | 1   | DI08 | D107 | DI06 | DI05 | D104 | DI03 | DIO2 | DIO1       | GPI |  |

|                        | DATA-OUT REGISTER |     |      |      |      |      |      |      |      |      |   |  |  |

|------------------------|-------------------|-----|------|------|------|------|------|------|------|------|---|--|--|

| ADDRESS BIT ASSIGNMENT |                   |     |      |      |      |      |      |      |      |      | 1 |  |  |

| RS2                    | RS1               | RS0 | D0   | D1   | D2   | D3   | D4 ` | D5   | D6   | D7   |   |  |  |

| 1                      | 1                 | 1   | DIO8 | DI07 | DI06 | DI05 | DI04 | DI03 | DI02 | DIO1 | G |  |  |

|     |     | -   | AUXIL | IARY- | COM | /AND | REGIS | STER |    |    |

|-----|-----|-----|-------|-------|-----|------|-------|------|----|----|

| ΑE  | DRE | SS  |       |       | BIT | ASS  | GNME  | NT   |    |    |

| RS2 | RS1 | RS0 | D0    | D1    | D2  | D3   | D4    | D5   | D6 | D7 |

| 0   | 1   | 1   | cs    | ХX    | xx  | f4   | f3    | f2   | f1 | fO |

Clear or Set

f4-f0 Auxiliary command select

|     |      | INT | ERRUI | PT MA | ASK/S | TATU | S REG | ISTER | 0   |     |

|-----|------|-----|-------|-------|-------|------|-------|-------|-----|-----|

| ΑŒ  | DDRE | SS  |       |       | BIT   | ASS  | IGNM  | NT    |     |     |

| RS2 | RS1  | RS0 | DO    | D1    | D2    | D3   | D4    | D5    | D6  | D7  |

| 0   | 0    | 0   | хx    | хx    | Bł    | во   | END   | SPAS  | RLC | MAC |

| 0   | 0    | 0   | INTO  | INT 1 | 81    | во   | END   | SPAS  | RLC | MAC |

INT1 Interrupt Status Register 1 END Last byte in string received

INTO Interrupt Status Register 0 SPAS Device has been serial polled ВІ Byte In

ВО Byte Out

RLC Remote/Local Change MAC My Address Change

|     |      | INT | ERRUI | PT MA | ASK/S | ratu: | S REGI | STER | 1   |     |            |

|-----|------|-----|-------|-------|-------|-------|--------|------|-----|-----|------------|

| A   | DDRE | SS  |       |       | BIT   | ASS   | IGNME  | NT   |     |     |            |

| RS2 | RS1  | RS0 | D0    | D1    | D2    | D3    | D4     | D5   | D6  | D7  |            |

| 0   | 0    | 1   | GET   | ERR   | UNC   | APT   | DCAS   | MA   | SRQ | IFC | INT MASK 1 |

| 0   | 0    | 1   | GET   | ERR   | UNC   | APT   | DCAS   | MA   | SRQ | IFC | INT STAT 1 |

GET Group Execute Trigger

ERR

UNC Unrecognized Command APT Address Pass Through

DCAS Device Clear Active State

SRQ Service Request MA My Address

**IFC** Interface Clear

|     |     |    | ADD | RESS | STA | TUS R | EGIST | ER   |      |      |

|-----|-----|----|-----|------|-----|-------|-------|------|------|------|

| AC  | DRE | SS |     |      | BIT | ASS   | GNME  | NT   |      |      |

| RS2 | RS1 |    |     |      |     |       | D4    |      |      | D7   |

| 0   | 1   | 0  | REM | LLO  | ATN | LPAS  | TPAS  | LADS | TADS | ulpa |

REM Remote State

LLO Local Lockout

ATN Attention

LPAS Listener Primary

TPAS Talker Primary Addressed State

LADS Addressed to listen

TADS Addressed to talk ulpa LSB last address

Addressed State

|     |      |     |      | ADD | RESS | REGIS | TER  |    |    |    |

|-----|------|-----|------|-----|------|-------|------|----|----|----|

| ΑI  | ODRE | SS  |      |     | BIT  | ASS   | GNME | NT |    |    |

| RS2 | RS1  | RS0 | DO   | D1  | D2   | D3    | D4   | D5 | D6 | D7 |

| 1   | 0    | 0   | edpa | dal | dat  | Α5    | Α4   | А3 | A2 | A1 |

edpa Enable dual-primary

Disable talker function dat A5-A1 Primary address

addressing mode Disable listener function

|            |     |      |     | В  | US S | TATUS | REGI | STER |    |     |     |

|------------|-----|------|-----|----|------|-------|------|------|----|-----|-----|

|            |     | DDRE |     |    |      |       | ASSI |      |    |     |     |

| INT MASK 0 | RS2 | RS1  | RSO | DO | Đ1   | D2    | D3   | D4   | D5 | D6  | D7  |

| INT STATO  | 0   | 1    |     |    |      | NDAC  |      |      |    | IFC | REN |

|     | SERIAL POLL REGISTER   |     |      |      |      |      |      |            |      |      |  |  |  |

|-----|------------------------|-----|------|------|------|------|------|------------|------|------|--|--|--|

| Α[  | ADDRESS BIT ASSIGNMENT |     |      |      |      |      |      |            |      |      |  |  |  |

| RS2 | RS1                    | RS0 | DO   | D1   | D2   | D3   | D4   | D5         | D6   | D7   |  |  |  |

| 1   | 0                      | 1   | S8   | rsv1 | S6   | S5   | S4   | <b>S</b> 3 | S2   | S1   |  |  |  |

|     |                        |     | DIO8 | D107 | DIO6 | DIO5 | DIO4 | DIO3       | DIO2 | DIO1 |  |  |  |

S8,S6-S1 Device Status

rsv1 Request Service bit 1

|         |     | СО  | MMAI | ND PA | LSS TI | HROU | GH RE | GIST | R    |            | ]  |

|---------|-----|-----|------|-------|--------|------|-------|------|------|------------|----|

| ADDRESS |     | SS  |      |       | BIT    | ASS  | GNME  | NT   |      |            |    |

| RS2     | RS1 | RS0 | D0   | D1    | D2     | D3   | D4    | D5   | D6   | <b>D</b> 7 |    |

| 1       | 1   | 0   | DI08 | DI07  | DI06   | DI05 | DI04  | DI03 | DI02 | DI01       | GF |

|     |      |     | PA   | RALL | EL PO | LL RE | GISTE | R    |      |      |

|-----|------|-----|------|------|-------|-------|-------|------|------|------|

| Αſ  | DDRE | SS  |      |      | BIT   | ASS   | GNME  | NT   |      |      |

| RS2 | RS1  | RS0 | DO   | D1   | D2    | D3    | D4    | D5   | D6   | D7   |

| 1   | 1    | 0   | PP8  | PP7  | PP6   | PP5   | PP4   | PP3  | PP2  | PP1  |

|     |      |     | DIO8 | DI07 | DI06  | DIO5  | DIO4  | DIO3 | DIO2 | DiO1 |

FIGURE 2. INTERNAL REGISTERS

# absolute maximum ratings over operating case temperature range (unless otherwise noted) $^\dagger$

| Supply voltage range VCC‡           | $\cdot$ . $-0.3$ V to 20 V |

|-------------------------------------|----------------------------|

| All input and output voltage ranges | $_{\odot}$ – 0.3 V to 20 V |

| Continuous power dissipation        | 1.0 W                      |

| Operating case temperature range    |                            |

| Storage temperature range           | – 55 °C to 150 °C          |

<sup>†</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

|                 |                            |                                  | MIN  | NOM | MAX          | UNIT |

|-----------------|----------------------------|----------------------------------|------|-----|--------------|------|

| Vcc             | Supply voltage             |                                  | 4.75 | 5   | 5.25         | V    |

| Vss             | Supply voltage             |                                  |      | 0   |              | V    |

| VIH             | High-level input voltage   |                                  | 2    |     |              | V    |

| VIL             | Low-level input voltage    |                                  |      |     | 0.8          | V    |

|                 |                            | All outputs except REN, IFC, INT |      |     | <b>- 400</b> | μΑ   |

| ЮН              | High-level output current  | REN, IFC only                    |      |     | - 100        | μΑ   |

| l <sub>OL</sub> | Low-level output current   | · .                              |      |     | 2            | mA   |

| TC              | Operating case temperature |                                  | - 55 |     | 110          | °C   |

## electrical characteristics over full range of recommended operating conditions

|          | PARAM                                     | ETER                        | TEST CONDITIONS                                              | MIN | TYP | MAX  | UNIT |

|----------|-------------------------------------------|-----------------------------|--------------------------------------------------------------|-----|-----|------|------|

| Voн      | High-level All outputs except REN,IFC,INT |                             | I <sub>OH</sub> = -400 μA                                    | 2.4 |     |      | ٧    |

| •        | output voltage                            | REN, IFC only               | $I_{OH} = -100  \mu A$                                       | 2.2 |     |      |      |

| VOL      | Low-level output voltage                  |                             | I <sub>OL</sub> = 2 mA                                       |     |     | 0.4  | V    |

| - II     | Input current (any input)                 |                             | $V_{CC} = 5.25 \text{ V}, V_{I} = V_{SS} \text{ to } V_{CC}$ |     |     | ± 10 | μΑ   |

| <u>'</u> |                                           |                             | $V_{CC} = 5.25 \text{ V}, V_{O} = 2.4 \text{ V}$             |     |     | 20   | μΑ   |

| loz      | Off-state output                          | t current                   | $V_{CC} = 5.25 \text{ V}, V_{O} = 0.4 \text{ V}$             |     |     | - 20 | μА   |

| ICC      | VCC supply current                        |                             | V <sub>CC</sub> = 5.25 V                                     |     |     | 200  | mA   |

| Ci       | Input capacitan                           | ce (any input) <sup>†</sup> | f = 1 MHz, all other<br>pins at 0 V                          |     |     | 15   | pF   |

<sup>&</sup>lt;sup>†</sup>Parameter guaranteed via characterization data.

<sup>&</sup>lt;sup>‡</sup>All voltage values in this data sheet are with respect to VSS.

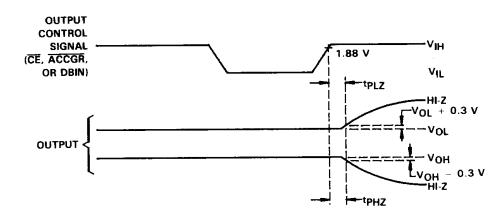

# clock and host interface timing requirements over full range of operating conditions

|                        |                              | MIN NOM MAX | UNIT |

|------------------------|------------------------------|-------------|------|

| <sup>†</sup> c(φ)      | Clock cycle time             | 200 2000    | ns   |

| tw(øH)                 | Clock high pulse duration    | 1955        | ns   |

| <sup>t</sup> w(¢L)     | Clock low pulse duration     | 45          | ns   |

| t <sub>su(AD)</sub>    | Address setup time           | 0           | ns   |

| t <sub>su</sub> (DBIN) | DBIN setup time <sup>†</sup> | 0           | ns   |

| <sup>†</sup> su(CE)    | CE setup time                | 100         | ns   |

| t <sub>su(WE)</sub>    | WE setup time <sup>†</sup>   | 0           | ns   |

| tw(WE)                 | WE low pulse duration        | 80          | ns   |

| <sup>t</sup> su(DA)    | Data setup time              | 80          | ns   |

| th(DA)                 | Data hold time               | 15          | ns   |

| th(AD)                 | Address hold time            | 0           | ns   |

| th(DBIN)               | DBIN hold time <sup>†</sup>  | 0           | ns   |

| <sup>†</sup> h(CE)     | CE hold time                 | 80          | ns   |

| <sup>t</sup> su(GR)    | ACCGR setup time             | 100         | ns   |

| th(GR)                 | ACCGR hold time              | 80          | ns   |

<sup>&</sup>lt;sup>†</sup>Parameter guaranteed via characterization data.

# host interface timing characteristics over full range of operating conditions

|                          | PARAMETER                             | MIN | NOM | MAX | UNIT |

|--------------------------|---------------------------------------|-----|-----|-----|------|

| ta(CE)                   | Access time from CE                   |     |     | 150 | ns   |

| ta(DBIN)                 | Access time from DBIN low             | ·   | •   | 150 | ns   |

| t <sub>su(AD)</sub>      | Address setup time to $\overline{CE}$ | 0   |     |     | ns   |

| <sup>t</sup> d(DBINL-DZ) | DBIN low to data high impedance       |     | 50  | 100 | ns   |

| <sup>†</sup> d(CEH-DZ)   | CE high to data high impedance        |     | 50  | 100 | ns   |

| ta(GR)                   | Access time from ACCGR low            |     | -   | 150 | ns   |

| td(AGRH-DZ)              | ACCGR high to data high impedance     |     | 50  | 100 | ns   |

| td(GRL-RQH)              | Delay of ACCRQ high from ACCGR low    |     |     | 100 | ns   |

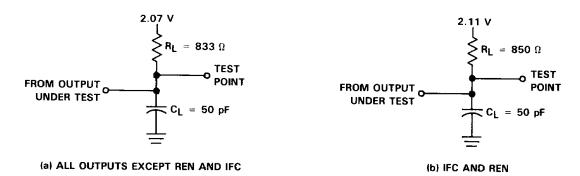

### PARAMETER MEASUREMENT INFORMATION

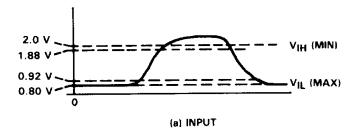

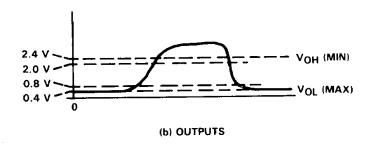

NOTE 1: Timing measurements are referenced to or from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted.

FIGURE 3. TEST LOAD CIRCUITS

FIGURE 4. VOLTAGE REFERENCE LEVELS

FIGURE 5. HIGH-IMPEDANCE MEASUREMENTS

### clock cycle timing

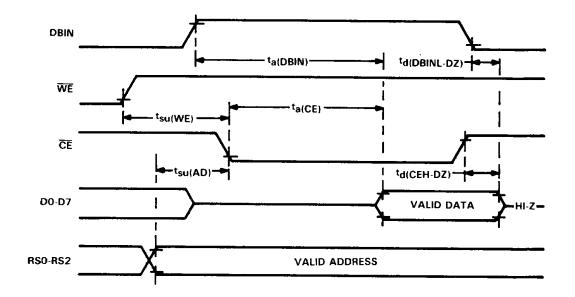

### read cycle timing

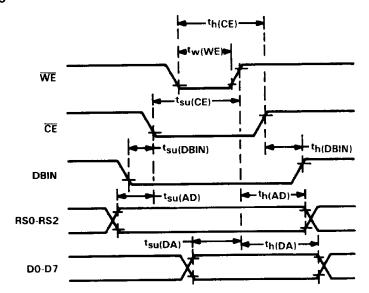

#### write cycle timing

NOTE 2: th(AD) and th(DA) are shown measured from the rising edge of WE. This is the correct reference point in this figure, since the measurements should be from the rising edge of WE or CE — whichever comes first.

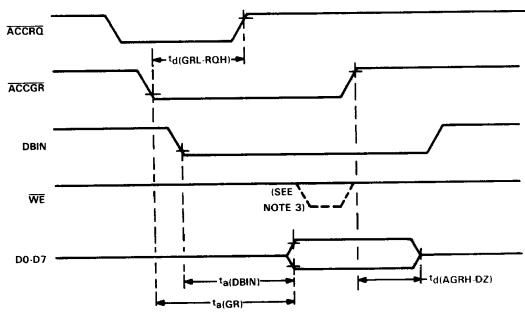

#### **DMA** read operation

NOTE 3: A write-enable pulse may occur in a DMA read operation. A write-enable pulse may therefore be provided for system memory and need not be suppressed at the SMJ9914A.

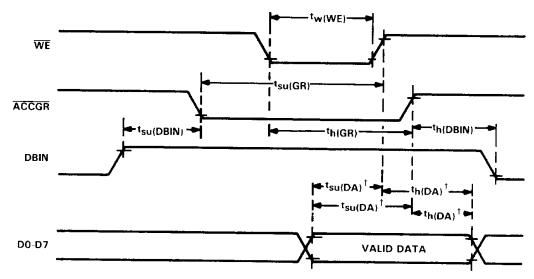

### **DMA** write operation

$<sup>^{\</sup>dagger}t_{SU(DA)}$  and  $t_{h[DA]}$  are only applicable to the first signal to become inactive, whether it is  $\overline{WE}$  or  $\overline{ACCGR}$ .

# source handshake timing characteristics over full range of operating conditions (see Note 4)

|                         | PARAMETER                           | TEST CONDITIONS                        | MIN            | MAX                   | UNIT        |

|-------------------------|-------------------------------------|----------------------------------------|----------------|-----------------------|-------------|

|                         | Delay of DAV true from end          | Normal T <sub>1</sub> (see Note 5)     | 12(φ)↑         | 12( <b>φ</b> )↑ + 310 | ns          |

| <sup>t</sup> d <b>1</b> | of write operation to               | Short T <sub>1</sub> (see Note 5)      | 8(φ)↑          | 8(φ)↑ + 310           | ns          |

| _                       | data out register                   | Very short T <sub>1</sub> (see Note 5) | 4( <b>φ</b> )↑ | 4( <b>φ</b> )↑ + 310  | ns          |

|                         | Delay of valid GPIB                 |                                        |                |                       | · · · · · · |

| t <sub>d2</sub>         | data lines from end of              |                                        |                | 140                   | ns          |

|                         | write cycle                         |                                        | i              |                       |             |

| t <sub>d</sub> 3        | Delay of BO interrupt from DAC true | BO interrupt unmasked                  |                | 300                   | ns          |

| t <sub>d4</sub>         | Delay of ACCRQ DAC true             |                                        |                | 300                   | ns          |

| t <sub>d</sub> 5        | Delay of DAV false from DAC true    |                                        |                | 160                   | ns          |

NOTES: 4. The timing of the source handshake is the same whether ATN is true or false; i.e., whether the device is in TACS, CACS, or SPAS.

5. A very short bus settling time (T<sub>1</sub>) occurs on the second and subsequent data byte when ATN is false if the "vstd1" feature is set. A slightly longer bus settling time takes place if "std1" is set unless there is a very short bus settling time. In all other instances, a normal bus settling time occurs.

# acceptor handshake timing characteristics over full range of operating conditions

|                  | PARAMETER                                                                | TEST CONDITIONS                                                                | MIN            | MAX                                                   | UNIT |

|------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------|-------------------------------------------------------|------|

| <sup>t</sup> d6  | Delay of BI interrupt<br>from DAV true                                   | BI interrupt unmasked,<br>ATN = false,<br>device in LACS                       | 2(♠)↑          | 2(φ)† + <b>41</b> 5                                   | ns   |

| t <sub>d</sub> 7 | Delay of ACCRQ from DAV true                                             | ATN = false,<br>device is in LACS                                              | 2(Φ)↑          | 2( <b>φ</b> )↑ + 290                                  | ns   |

| t <sub>d8</sub>  | Delay of NDAC false from DAV true                                        | ATN = false,<br>device in LACS                                                 | 3(φ)↑          | 3(φ)↑ + 445                                           | ns   |

| t <sub>d</sub> 9 | Delay of NRFD false from<br>end of read operation<br>of Data-In register | ATN = false,<br>device is in LACS                                              |                | 220                                                   | ns   |

| <sup>‡</sup> d10 | Delay of interface<br>message interupt<br>from DAV true                  | ATN = false, device not in CACS, all interface message interrupts {except UNC} | <b>2(φ)</b> †  | 2(φ)↑ + 415                                           | ns   |

| t <sub>d11</sub> | Delay of NDAC false<br>from DAV true                                     | UNC interrupt only  ATN = true, device not in CACS, no DAC holdoff             | 5(φ)↑<br>7(φ)↑ | $\frac{5(\phi)\uparrow + 415}{7(\phi)\uparrow + 415}$ | ns   |

| t <sub>d12</sub> | Delay of NDAC false<br>from end of write<br>operation                    |                                                                                |                | 230                                                   | ns   |

| t <sub>d13</sub> | Delay of NRFD false<br>from DAV false                                    | ATN = true,<br>device not in CACS                                              |                | 180                                                   | ns   |

NOTE 6: The interrupts generated by interface messages are shown in Table 3-15 of the TMS9914A General Purpose Interface Bus (GPIB) Controller Data Manual (MP033A).

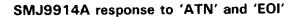

# ATN, EOI, and IFC timing characteristics over full range of operating conditions

|                  | PARAMETER                         | TEST CONDITIONS        | MIN                 | MAX                 | UNIT |

|------------------|-----------------------------------|------------------------|---------------------|---------------------|------|

| td14             | Delay of NDAC true from ATN true  | Device is not in CACS  |                     | 195                 | ns   |

| t <sub>d15</sub> | Delay of TE high from EOI true    | Device is not in CACS  |                     | 125                 | ns   |

| td16             | Delay of valid data from EOI true | Device is not in CACS  |                     | 140                 | ns   |

| td17             | Delay of TE low from EOI false    | Device is not in CACS  |                     | 125                 | ns   |

| t <sub>d18</sub> | Delay of NRFD true from ATN false | Device is in LADS/LACS |                     | 140                 | ns   |

| <sup>t</sup> d19 | Response time to IFC              |                        | 16t <sub>c(0)</sub> | 30t <sub>c(0)</sub> | ns   |

### SMJ9914A GPIB CONTROLLER

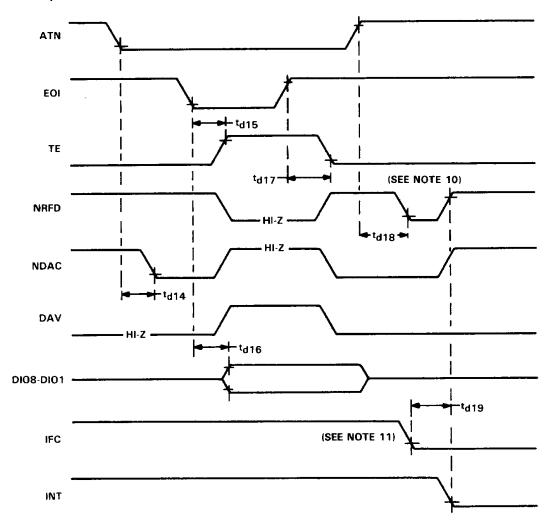

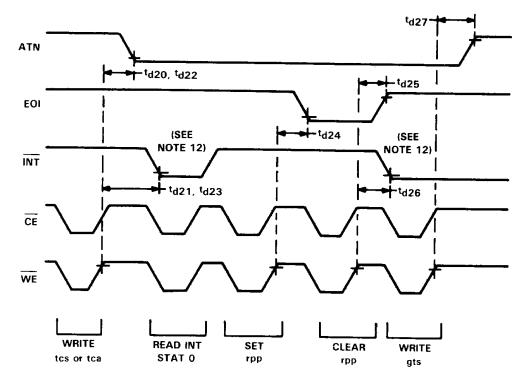

# controller timing characteristics over full range of operating conditions

|                  | PARAMETER                                                     | TEST CONDITIONS                   | MIN                 | MAX                           | UNIT |

|------------------|---------------------------------------------------------------|-----------------------------------|---------------------|-------------------------------|------|

| <sup>t</sup> d20 | Delay of ATN true<br>from end of tca<br>auxiliary command     |                                   | 8t <sub>c(0)</sub>  | 10(φ)1 + 220                  | ns   |

| <sup>t</sup> d21 | Delay of BO interrupt<br>from end of tca<br>auxiliary command |                                   | 18t <sub>c(0)</sub> | 22( <b>ø</b> )↑ + <b>41</b> 5 | ns   |

| <sup>t</sup> d22 | Delay of ATN true<br>from end of tcs<br>auxiliary command     | BO unmasked,<br>device is in ANRS | 8 <sub>tc(0)</sub>  | 10(¢)↑ + 220                  | пѕ   |

| <sup>t</sup> d23 | Delay of BO interrupt<br>from end of tcs<br>auxiliary command | BO unmasked,<br>device is in ANRS | 18t <sub>c(0)</sub> | 22( <b>ø</b> )† + 415         | ns   |

| <sup>t</sup> d24 | Delay of EOI true from rpp auxiliary command set              |                                   |                     | 230                           | ns   |

| <sup>t</sup> d25 | Delay of EOI false from rpp auxiliary command set             |                                   |                     | 230                           | ns   |

| <sup>t</sup> d26 | Delay of BO interrupt from rpp auxiliary command cleared      | BO unmasked                       | 8t <sub>c(0)</sub>  | 10(φ)† + 415                  | ns   |

| t <sub>d27</sub> | Delay of ATN false from gts auxiliary command                 | Device is not in SDYS or STRS     |                     | 210                           | ns   |

Downloaded from **Datasheet.su**

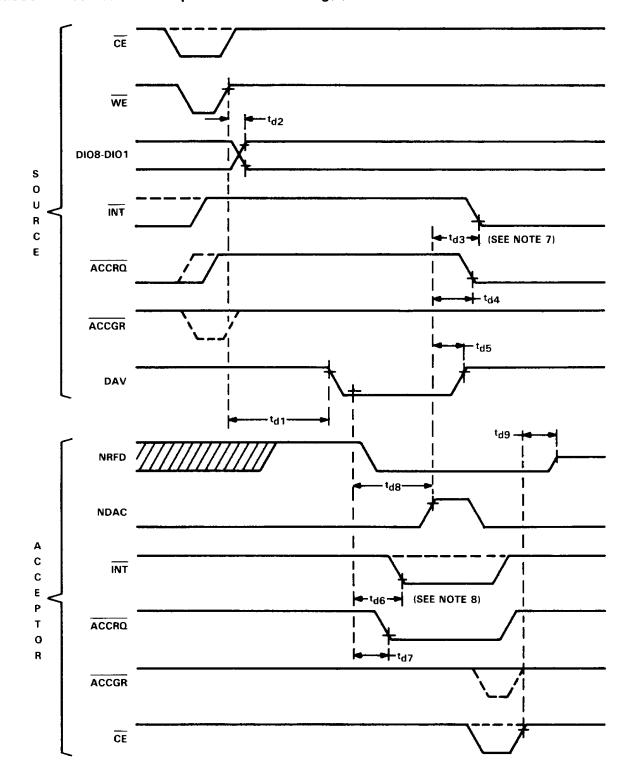

### SMJ9914A source and acceptor handshake timing(s)

NOTES: 7. The interrupt line is taken low by a BO interrupt.

8. The interrupt line is taken low by a BI interrupt.

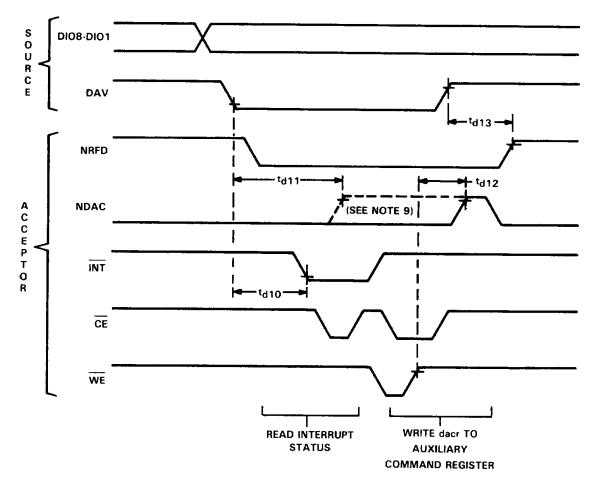

# SMJ9914A acceptor handshake timing "ATN" true

NOTE 9: The broken line shows the waveform if there is no DAC holdoff. The solid lines assume there is a DAC holdoff.

NOTES: 10. This assumes that an RFD holdoff occurs.

11. IFC causes the SMJ9914A to be unaddressed and an IFC interrupt occurs.

### SMJ9914A controller timing

NOTE 12: A BO interrupt occurs as the SMJ9914A enters CACS.